AMD EPYC Venice: campioni Zen 6 con fino a 192 core emergono dai test di validazione

Le prime immagini dei processori server AMD EPYC Venice basati su architettura Zen 6 confermano configurazioni fino a 192 core, piattaforme Congo, Kenya e Nige…

Contenuto

Scopri anche

- AMD porta la piattaforma Helios in India: 72 GPU MI455X per rack con 2,9 exaflop FP4

- AceMagic lancia Retro X5, il mini PC con design NES e processore AMD Ryzen AI 9

- Nvidia domina il mercato degli acceleratori AI con quota superiore all'80% e proiezioni di crescita sostenuta

- Intel 18A e la strategia di recupero: produzione USA, partnership AI e sfide nel foundry

- AMD definisce le "Agent Computer" come nuova frontiera dell'AI PC

- Samsung e AMD firmano accordo strategico per memoria AI di nuova generazione

- Intel's Strategic Acquisition of SambaNova Systems and Market Position

- CoWoS e HBM: i colli di bottiglia dell'infrastruttura AI nel 2026

- Il ritorno delle CPU nei data center: l'infrastruttura server nell'era dell'AI agente

- Samsung e AMD stringono accordo strategico per memoria HBM4 e soluzioni AI di nuova generazione

- AMD Q4 2025: Centro Dati e AI al Centro delle Attese degli Analisti

- Nvidia e la nuova definizione di AGI: quando l'intelligenza artificiale genera valore economico

- Meta svela la roadmap di quattro nuovi chip MTIA: infrastruttura AI interna entro il 2027

- Ordine da 300 milioni di dollari per server AMD con raffreddamento a diamante sintetico

- Il business networking di Nvidia supera i 31 miliardi di dollari e ridefinisce l'architettura dei data center AI

- Intel: la rinascita dei chip AI spinge il titolo ai massimi biennali

- Nvidia presenta il modulo Space-1 Vera Rubin per data center orbitali

- L'ascesa delle CPU nei data center AI: il nuovo ruolo dell'infrastruttura di calcolo

- Duke Energy: monitoraggio interruzioni corrente e strategie di gestione

- CIQ e AMD collaborano per ottimizzare Rocky Linux per carichi di lavoro AI e HPC

Campioni engineering di AMD EPYC Venice con architettura Zen 6 rilevati in benchmark online

- Architettura Zen 6 e varianti core density

- Dettagli delle piattaforme di test

- Configurazione memoria e specifiche I/O

- Processo produttivo TSMC N2 e efficienza energetica

- Nuove estensioni istruzioni e cache L3

- Socket SP7 e roadmap di rilascio

- Confronto generazioni EPYC

- Piattaforma consumer Olympic Ridge

- Implicazioni e scenari

- Cosa monitorare

- Fonti

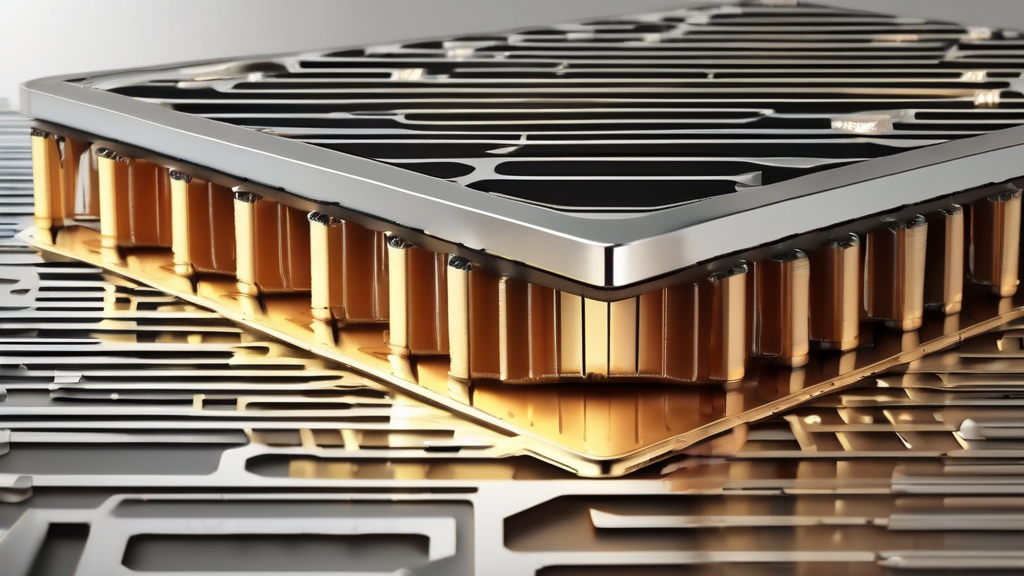

Sei risultati di test pubblicati su OpenBenchmark.org hanno rivelato i primi campioni engineering dei processori server AMD EPYC di sesta generazione, codenome Venice, basati sull'architettura Zen 6. I risultati, scoperti dall'utente Olrak29_ su X, mostrano configurazioni che spaziano da 64 a 192 core, testate su tre piattaforme interne identificate con i nomi in codice Congo, Kenya e Nigeria.

Architettura Zen 6 e varianti core density

⬆ Torna suSecondo le informazioni emerse, i campioni EPYC Venice utilizzano core Zen 6c ad alta densità. I modelli da 64 e 128 core presentano 32 core per CCD (Core Complex Die), mentre le varianti da 192 core integrano 24 core per CCD. Questa configurazione conferma quanto anticipato da precedenti report sull'aumento della densità di core per CCD nell'architettura Zen 6 rispetto a Zen 5.

La documentazione tecnica indica che Zen 6c, nome in codice "Monarch", rappresenta la variante ad alta densità core destinata ai processori server e probabilmente anche alle piattaforme mobili. Ogni CCD standard Zen 6 ospiterà fino a 12 core, mentre i CCD Zen 6c potranno arrivare a 32 core, consentendo configurazioni massime fino a 256 core per i modelli datacenter di punta.

Dettagli delle piattaforme di test

⬆ Torna suLa piattaforma Congo ha mostrato due configurazioni: un modello da 192 core con 8 CCD e 2 IOD (I/O Die), e una variante da 64 core con 2 CCD e 2 IOD. La piattaforma Kenya presenta un processore da 128 core con 4 CCD e 2 IOD. La piattaforma Nigeria è configurata come sistema dual socket (2P), con sei campioni testati in configurazioni che vanno da 64 a 192 core per processore.

I codici identificativi dei campioni engineering includono 100-000001053-03 e 100-000001051-08 per le versioni da 192 core con 384 thread, mentre i modelli 100-000001056-09 e 100-000001056-03 corrispondono alle varianti da 128 core con 256 thread.

Configurazione memoria e specifiche I/O

⬆ Torna suI benchmark rilevano supporto memoria DDR5-6400 e DDR5-8000, con configurazioni che prevedono moduli da 64 GB e 128 GB. La presenza di velocità DDR5-8000 in alcuni test suggerisce una fase iniziale di platform bring-up, con specifiche non ancora finalizzate. AMD e Samsung hanno confermato la collaborazione su memoria DDR5 ad alte prestazioni per la sesta generazione EPYC, coerente con le rilevazioni di DDR5-8000 nei benchmark.

Secondo i leak, i processori Venice supporteranno fino a 16 canali memoria DDR5-6400 per i modelli SP7 di punta, con 128 lane PCIe Gen 5 e 64 lane PCIe Gen 6. Le varianti mid-range integrano 8 canali memoria DDR5-6400, mentre le configurazioni entry-level mantengono 4 canali. La larghezza di banda memoria per la piattaforma Helios, che combinerà processori Venice con acceleratori Instinct, raggiunge fino a 1,6 TB/s.

Processo produttivo TSMC N2 e efficienza energetica

⬆ Torna suAMD ha confermato che Venice sarà il primo prodotto HPC realizzato sul nodo N2 (2nm) di TSMC. I CCD vengono prodotti sul processo 2nm-class, mentre gli IOD utilizzano un derivato del processo 4nm. Il passaggio al nodo 2nm rappresenta un avanzamento significativo in termini di efficienza e densità rispetto alle generazioni precedenti.

I documenti tecnici indicano un TDP fino a 600W per i modelli SP7 di fascia alta, rispetto ai 400W degli EPYC 9005 "Turin" basati su Zen 5. Questo incremento termico suggerisce che le soluzioni di raffreddamento tradizionali potrebbero raggiungere i loro limiti, rendendo necessario il Direct Liquid Cooling per le configurazioni più potenti.

Nuove estensioni istruzioni e cache L3

⬆ Torna suL'architettura Zen 6 introduce nuove estensioni istruzioni, tra cui AVX512_BMM, AVX_NE_CONVERT, AVX_IFMA, AVX_VNNI_INT8 e AVX512_FP16. La piattaforma sarà la prima a supportare FRED (Fast Register Enumeration and Delivery). La capacità cache L3 aumenta a 48MB per i CCD Zen 6, mentre i modelli Zen 6c dovrebbero integrare 2MB L3 per core, ottimizzati per carichi di lavoro multipli di piccole dimensioni.

Socket SP7 e roadmap di rilascio

⬆ Torna suVenice utilizzerà il nuovo socket SP7 per i modelli high-end e SP8 per le varianti scale-out e entry-level. La piattaforma SP7 supporta configurazioni fino a 8 CCD Zen 6, raggiungendo i 256 core massimi. L'architettura SP7 è progettata per HPC, consolidamento VM massivo e workload ad alta parallelizzazione.

Secondo la roadmap AMD presentata a luglio 2024, Zen 6 ha come obiettivo il lancio tra fine 2026 e inizio 2027. I campioni engineering attualmente in circolazione indicano che il silicon è già in fase di validazione presso i partner. AMD non ha ancora confermato ufficialmente le specifiche definitive né la data di disponibilità commerciale.

Confronto generazioni EPYC

⬆ Torna suLa tabella seguente riassume il confronto tra le generazioni EPYC documentate nelle fonti:

EPYC 9005 "Turin" (Zen 5): fino a 128 core, 16 CCD con 8 core ciascuno, socket SP5, TDP 500W.

EPYC 9005 "Turin" (Zen 5c): fino a 192 core, 12 CCD con 16 core ciascuno, socket SP5, TDP 500W.

EPYC 9006 "Venice" (Zen 6): fino a 128 core per CCD standard, socket SP7/SP8, TDP fino a 600W.

EPYC 9006 "Venice" (Zen 6c): fino a 256 core, 8 CCD con 32 core ciascuno, socket SP7, TDP fino a 600W.

Piattaforma consumer Olympic Ridge

⬆ Torna suPer il mercato consumer, Zen 6 utilizzerà il nome in codice "Medusa" per i processori desktop, che dovrebbero essere commercializzati come Ryzen 10000. La piattaforma consumer porta il nome in codice "Olympic Ridge". AMD non ha confermato una data di rilascio per Olympic Ridge, ma le generazioni precedenti hanno visto i prodotti consumer arrivare prima di quelli server. L'attuale roadmap indica che Venice potrebbe precedere Olympic Ridge, coerente con la strategia AMD di capitalizzare sulla domanda rinnovata del datacenter.

Questo articolo è una sintesi basata esclusivamente sulle fonti elencate.

Implicazioni e scenari

⬆ Torna suL'emergenza di campioni engineering già in validazione suggerisce che AMD sta accelerando lo sviluppo di Venice per consolidare la propria posizione nel mercato datacenter. L'incremento dei core fino a 256 unità e il passaggio al nodo TSMC N2 potrebbero ridefinire gli standard di densità computazionale, con conseguenze rilevanti per carichi di lavoro virtualizzati e HPC.

- Scenario 1: Se i modelli SP7 da 256 core raggiungessero il mercato con specifiche definitive coerenti ai leak, AMD potrebbe estendere il vantaggio competitivo nei segmenti ad alta parallelizzazione.

- Scenario 2: Il TDP fino a 600W potrebbe rendere il Direct Liquid Cooling una requisito pratico per le configurazioni di punta, influenzando le decisioni di investimento infrastrutturale dei datacenter.

- Scenario 3: La transizione verso socket SP7 e SP8 potrebbe determinare un ciclo di rinnovo delle piattaforme, con impatti sui tempi di adozione da parte degli integratori.

Cosa monitorare

⬆ Torna su- Conferma ufficiale delle specifiche DDR5 definitive e relative velocità supportate.

- Stato di avanzamento della validazione dei campioni engineering presso i partner.

- Indicazioni sui tempi di disponibilità commerciale e allineamento con la roadmap prevista.

Nota editoriale: questa sezione propone una lettura analitica dei temi trattati, senza introdurre dati fattuali non presenti nelle fonti.

Fonti

⬆ Torna su- https://www.tomshardware.com/pc-components/cpus/amd-zen-6-venice-es-chips-break-cover-with-up-to-192-cores-32-per-ccd-in-early-stress-test-kenya-congo-nigeria-platforms-leaked

- https://www.guru3d.com/story/amd-epyc-venice-samples-appear-with-up-to-192-zen-6-cores/

- https://xanxogaming.com/noticias/amd-epyc-venice-muestras-zen-6-nucleos-congo-kenya-nigeria/

- https://en.wikipedia.org/wiki/Zen_6

- https://hardwaretimes.com/amd-zen-6-venice-leak-2nm-node-256-cores-16-ch-ddr5-6400-and-208-pcie-gen-56-lanes/

- https://www.igorslab.de/en/amd-epyc-9006-venice-zen-6-zen-6c-with-up-to-256-cores-approaching/

In breve

- amd

- processor

- datacenter

- tsmc